# Tuning Verilog-A PSP Model to a Specific Technology

Ivan Valentinov Petkov, George Vasilev Angelov, Ivan Dimitrov Panayotov and Marin Hristov Hristov

Abstract – The method of tuning a Verilog-A PSP model to a specific technology is presented in this paper. The mechanisms of defining the required model parameters, their extraction, and the implementation of the respective changes in Verilog-A are described. New program tool for extraction (Extract CAD) is utilized together with CADENCE Spectre simulator for the circuit simulations of the Verilog-A code.

*Keywords* – PSP model, Verilog-A, CADENCE, Extract CAD, parameter extraction, simulation.

#### I. Introduction

PSP Model

Modeling is at the core of any design process. Compact MOSFET models are an essential bridge between the fabrication process development and the circuit design. Their primary function is to accurately reproduce the device characteristics in details, which are essential to the design of digital, analog, mixed-signal, and RF integrated circuits. There is a wide consensus in the compact modeling community that traditional threshold-voltagebased models of MOSFETs need to be replaced with the more advanced surface-potential-based or inversioncharge- based models [1]). One of the motivations for choosing the surface-potential-based approach is that it enables the physical modeling of the device. Despite the clear physics and the ability to provide a single expression for all regions of operation [2] surface-potential-based models did not become popular until the last decade due, in part, to their perceived complexity. Successful surfacepotential-based models became possible only after significant progress was made in the techniques for the computing the surface potential, simplification of the charge equations and the introduction of small-geometry effects. The implementation of these advances and the overall model structures of SP [3] and MM11 [4] turned out to be compatible, enabling the merger of both models into a single new model called PSP that combines the

Ivan Petkov is with the Department of Electronics and Electronics Technologies, Faculty of Microelectronics, Technical University - Sofia, 8 Kliment Ohridski blvd., 1000 Sofia, Bulgaria, e-mail: ivp@ecad.tu-sofia.bg

George Angelov is with the Department of Electronics and Electronics Technologies, Faculty of Microelectronics, Technical University - Sofia, 8 Kliment Ohridski blvd., 1000 Sofia, Bulgaria, e-mail: gva@ecad.tu-sofia.bg

Ivan Panayotov is with the Department of Electronics and Electronics Technologies, Faculty of Microelectronics, Technical University - Sofia, 8 Kliment Ohridski blvd., 1000 Sofia, Bulgaria, e-mail: idp@ecad.tu-sofia.bg

Marin Hristov is with the Department of Electronics and Electronics Technologies, Faculty of Microelectronics, Technical University - Sofia, 8 Kliment Ohridski blvd., 1000 Sofia, Bulgaria, e-mail: mhristov@ecad.tu-sofia.bg

features of SP and MM11.

The major features of PSP include: physical surfacepotential-based formulation in both intrinsic and extrinsic model modules, physical and accurate description of the accumulation region, inclusion of all relevant small geometry effects, modeling of the halo implant effects, including the output conductance degradation in long devices, Coulomb scattering and non-universality in the mobility model, non-singular velocity-field relation the modeling of RF distortions including enabling intermodulation effects complete (IM3),symmetry, mid-point bias linearization enabling accurate modeling of the ratio-based circuits (e.g. R2R circuits), quantum-mechanical corrections, correction for the polysilicon depletion effects, GIDL/GISL model, surfacepotential-based noise model including channel thermal noise, flicker noise and channel-induced gate noise, advanced junction model including trap-assisted tunneling, band-to-band tunneling and avalanche breakdown, splinecollocation-based NOS model including all terminal currents, stress model [1].

The model structure consists of a core and enhancement blocks. The core block contains the quasi-static (OS) intrinsic and the extrinsic models. The intrinsic model contains expressions for the drain current, terminal charges and the noise sources. The extrinsic model includes contributions of the source-drain overlap regions, gate and substrate currents, etc. The enhancement block contains junction model developed using the NQS module [5, 6]. PSP distinguish between local and global model Global parameters include geometry dependences and before evaluating MOSFET output characteristics are converted into a small number (about 35) of local parameters actually used in the core model. The actual local parameters used in circuit simulations are then recomputed from the global parameters.

Verilog-A

Verilog-A is the analog extension to the Verilog hardware description language. It provides the ability to describe analog functions of electronic circuits behaviorally by means of mathematical equations, or conditional signal assignments. The use of Verilog-A for implementation of sophisticated models speeds up the design time and simulation process. Verilog-A is embedded in CADENCE Specter simulator which makes it easy to create and include custom model cells.

This paper focuses on the method of implementation of the DC core of the PSP compact model in Cadence Design Systems using Verilog-A HDL. The procedure for parameter extraction from standard CMOS technology is presented and the respective implementation of these parameters to the PSP model card is given. Extract CAD tool is used for the extraction process.

# II. MODEL ADAPTATION AND PARAMETERS EXTRACTION

The Verilog-A PSP model gives a general pattern for transistor parameters. The use of HDL-AMS provides the ability to easily tune up model parameters for a specific technology. For this reason the model parameter values are required.

Verilog-A PSP code is supported by Arizona State University and NXP Semiconductors [8]. Since its code is open it allows the flexibility of custom applications. One option is to take the free code from the developer site and to implement as individual library cell; this cell can afterwards be treated as global cell that is parameterized with specific parameters for each instance. The other option is to modify the free code hardcoding the parameters of a given technology; thus each instance complies with the parameter set of the chosen technology and is applicable for designs with this particular technology only.

A part of this research aims to obtain a set of *local* parameters for a particular NMOS device from a given technology. Once this set is obtained the PSP Verilog-A code is edited and compiled in Cadence Analog Environment in order to produce simulation data.

In this paper the Extract CAD software is used [9]. The Extract CAD software allows receiving the model card with local parameters for a specific device based on the input technology parameters and simulation data. This tool provides the ability to extract and tune up the local PSP model parameters. This program requires minimal number of process parameters, needed to define basic characteristics of the technology used. The values of the process parameters that are not explicitly given in the technology specifications are calculated by appropriate techniques. Both parameters are given in Table 1. In this research the AMS CMOS 0.35 technology along with CADENCE simulation environment is used.

TABLE 1. CALCULATED PROCESS PARAMETERS

| Name  | Unit               | Calculated           | Min        | Max       | Description              |  |  |  |

|-------|--------------------|----------------------|------------|-----------|--------------------------|--|--|--|

|       | Process Parameters |                      |            |           |                          |  |  |  |

| VFB   | V                  | -1                   | -          | -         | Flat-band voltage at TR  |  |  |  |

| TOX   |                    | 7,6 10 <sup>-9</sup> | $10^{-10}$ | -         | Gate oxide thickness     |  |  |  |

|       |                    | $2,12.10^{23}$       | $10^{20}$  | $10^{26}$ | Substrate doping         |  |  |  |

| NP    | m <sup>-3</sup>    | 727                  | 0          | -         | Gate poly-silicon doping |  |  |  |

| TOXOV | m                  | 7,6 10 <sup>-9</sup> | $10^{-10}$ | -         | Overlap oxide thickness  |  |  |  |

Other data required by the Extract CAD tool is that provided by the DC characteristics of the transistor with specific instance parameters. As this kind of information is not directly given it was provided by means of device simulations in CADENCE simulation environment.

# Parameters extraction

Process parameter values given in Table 1 are taken from the technology process data where available. Those that are not directly defined are obtained by calculations and simulation indirectly.

The parameter  $V_{\text{FB}}$  is obtained with simulations according to the method proposed by Dieter K. Schroder in

[7], by tracing the C-V characteristic of the transistor. The required value of  $V_{FB}$  is equal to the value of the gate voltage at a specific point of the curve.

The poly-silicon gate doping NP is calculated based on its relation to other device process parameters and their physical dependencies.

The DC characteristics are obtained by simulations with the AMS CMOS 0.35  $\mu m$  model in CADENCE. The device used is NMOS with channel width and length of 10  $\mu m$  and 315  $\mu m$  respectively. The simulated characteristics for the extraction process are:

- output characteristic Id (Vds) @ Vgs, and

- transfer characteristic Id (Vgs) @ Vbs.

The received simulation data is transferred to the Extract CAD software as a text file.

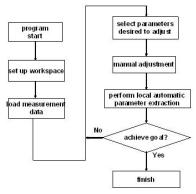

The flowchart on Figure 1 depicts a step-by-step guideline for software usage.

Figure 1. Workflow chart of Extract CAD tool.

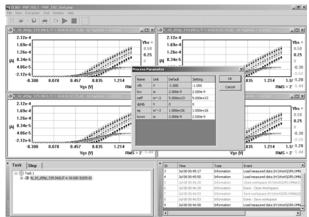

On Figure 2 DC characteristics in text format and waveforms from CADENCE are illustrated. The text file is fed as an input for the extraction program.

Figure 2. DC characteristics in text format.

In order to begin optimization process accurate values for process parameters are required. After calculation of the parameter values they are input in the extraction tool for further tuning purposes. The program window is given on Figure 3.

An important step is to choose the parameters which will be used in the process of optimization. The PSP 102.1 model has 70 such parameters. If all the parameters are used in optimization process this may result in lack of convergence. To ensure convergence we choose only the parameters with most significant influence on the characteristics. This is determined experimentally. The parameters that are to be fitted are given in Table 2.

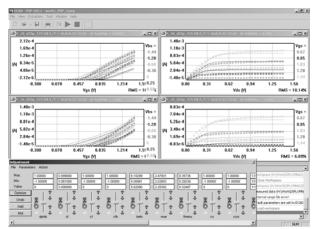

A comparison of the optimization results is given on Figure 4.

TABLE 2. PART OF THE MODEL PARAMETERS FITTED.

| NT                             | T T : /              | D-f-, 1                       | N. //:                                   | ъ.т         | Diti                                     |  |  |  |  |

|--------------------------------|----------------------|-------------------------------|------------------------------------------|-------------|------------------------------------------|--|--|--|--|

| Name                           | Unit                 |                               |                                          |             | Description                              |  |  |  |  |

| VED                            | h 7                  | Process                       | Paran                                    | ieters      |                                          |  |  |  |  |

| VFB                            | V                    | -1                            | _                                        | -           | Flat-band voltage at                     |  |  |  |  |

| TOV                            |                      | 7 6 10-9                      | 10-10                                    | -           | TR Gate oxide thickness                  |  |  |  |  |

| TOX<br>NEFF                    | m<br>-3              | $7.6 \cdot 10^{-9}$           | 10 10 10 10 10 10 10 10 10 10 10 10 10 1 | -<br>1 0+26 |                                          |  |  |  |  |

|                                | m <sup>-3</sup>      | 2.12·10 <sup>+23</sup><br>586 |                                          | 10          | Substrate doping                         |  |  |  |  |

| NP                             | m <sup>-3</sup>      | 586                           | 0                                        | -           | Gate poly-silicon                        |  |  |  |  |

| TOXOV                          |                      | 7.6·10 <sup>-9</sup>          | 10-10                                    |             | doping<br>Overlap oxide                  |  |  |  |  |

| IOXOV                          | m                    | 7.0.10                        | 10                                       |             | thickness                                |  |  |  |  |

| CT                             | -                    | 0                             | 0                                        |             |                                          |  |  |  |  |

| CT<br>NOV                      | -<br>m <sup>-3</sup> | $5 \cdot 10^{+25}$            | $0 \\ 10^{+20}$                          | 10+27       | Interface states factor                  |  |  |  |  |

| NOV                            | m                    | 5.10                          | 10                                       | 10          | Effective doping for                     |  |  |  |  |

| DDIJID                         | X 7                  | 0                             |                                          |             | overlap region                           |  |  |  |  |

| DPHIB                          | V<br>V <sup>-1</sup> | 0                             | -                                        | 1           | Offset of Phi_beta                       |  |  |  |  |

| DNSUB                          | V                    | 0                             | 0                                        | 1           | Effective doping bias-                   |  |  |  |  |

| NSLP                           | V                    | 0.05                          | 10 <sup>-3</sup>                         |             | dependence parameter                     |  |  |  |  |

| NSLP                           | V                    | 0.05                          | 10                                       | _           | Effective doping bias-                   |  |  |  |  |

| VAIGUD                         | <b>X</b> 7           | 0                             |                                          |             | dependence parameter                     |  |  |  |  |

| VNSUB                          | V                    | 0                             | _                                        | -           | Effective doping bias-                   |  |  |  |  |

|                                |                      | DIDI I                        |                                          | . 4         | dependence parameter                     |  |  |  |  |

| CF                             | <b>x</b> 7-1         | DIBL I                        |                                          | eters       | DIDI                                     |  |  |  |  |

| CF<br>CFB                      | V<br>v 7-1           | 0                             | 0                                        | 1           | DIBL parameter                           |  |  |  |  |

| СГВ                            | V                    | U                             | 0                                        | 1           | Back-bias dependence of CF               |  |  |  |  |

|                                |                      | N. J. 1114                    | D                                        | 4           |                                          |  |  |  |  |

| BETN                           | m <sup>2</sup> /V/s  | Mobility                      | Paran                                    |             | Product of channel                       |  |  |  |  |

| BEIN                           | m <sup>-</sup> / V/S | /·10 -                        | U                                        | <u> </u>    |                                          |  |  |  |  |

|                                |                      |                               |                                          |             | aspect ratio and Zero                    |  |  |  |  |

| MILE                           | /\ 1                 | 0.5                           | 0                                        |             | field mobility at TR  Mobility reduction |  |  |  |  |

| MUE                            | m/V                  | 0.5                           | 0                                        | -           | coefficient at TR                        |  |  |  |  |

| THEMU                          |                      | 1.5                           | 0                                        |             | Mobility reduction                       |  |  |  |  |

| THEMIO                         | -                    | 1.3                           | U                                        | -           | coefficient at TR                        |  |  |  |  |

| CS                             |                      | 0                             | 0                                        |             | Coulomb scattering                       |  |  |  |  |

| CS                             | _                    | U                             | U                                        | Ī           | parameter at TR                          |  |  |  |  |

| XCOR                           | $V^{-1}$             | 0                             | 0                                        |             | Non-universality                         |  |  |  |  |

| ACOK                           | <b>V</b>             | U                             | U                                        | Ī           | parameter                                |  |  |  |  |

| FETA                           |                      | 1                             | 0                                        |             | Effective field                          |  |  |  |  |

| FEIA                           | _                    | 1                             | U                                        | Ī           | parameter                                |  |  |  |  |

| Cha                            | nnal I a             | nath Modi                     | ılətion                                  | (CI N       | M) Parameters                            |  |  |  |  |

| ALP                            | L                    | 0.01                          | 0                                        | L           | CLM pre-factor                           |  |  |  |  |

| ALP1                           | V                    | 0.01                          | 0                                        |             | CLM enhancement                          |  |  |  |  |

| . 1111                         | [                    | Ĭ                             |                                          |             | factor above threshold                   |  |  |  |  |

| ALP2                           | $V^{-1}$             | 0                             | 0                                        | L           | CLM enhancement                          |  |  |  |  |

| 11112                          | •                    |                               | 9                                        | Ī           | factor below threshold                   |  |  |  |  |

| VP                             | V                    | 0.05                          | 10-10                                    |             | CLM logarithmic                          |  |  |  |  |

| 1                              | ľ                    | 0.03                          | 10                                       | [           | dependence parameter                     |  |  |  |  |

| Velocity Saturation Parameters |                      |                               |                                          |             |                                          |  |  |  |  |

| THESAT                         | V <sup>-1</sup>      | 1                             | 0                                        | Larai       | Velocity Saturation                      |  |  |  |  |

| TILDAI                         | ľ                    |                               | 3                                        | [           | Parameter at TR                          |  |  |  |  |

| THESATB                        | $V^{-1}$             | 0                             | -0.5                                     | 1           | Back-bias dependence                     |  |  |  |  |

| TILDAID                        | ľ                    |                               | 0.5                                      | 1           | of velocity saturation                   |  |  |  |  |

| THESATG                        | $V^{-1}$             | 0                             | -0.5                                     | t           | Gate-bias dependence                     |  |  |  |  |

| IIILSAIG                       | [                    |                               | -0.5                                     | ſ           | of velocity saturation                   |  |  |  |  |

| Saturation Voltage Parameter   |                      |                               |                                          |             |                                          |  |  |  |  |

| AX                             |                      | 3                             | 2                                        | _ 41 41     | Linear/saturation                        |  |  |  |  |

| * ***                          |                      |                               | Ĩ                                        |             | transition factor                        |  |  |  |  |

|                                | 1                    | 1                             | 1                                        | 1           | a amondon ractor                         |  |  |  |  |

For each parameter the minimum and maximum values has to be specified. This again is done according to the influence of each parameter to the characteristic curves. Some of these values are directly taken from the PSP model documentation as given parameter limitation.

Figure 3. DC characteristics visualization in Extract CAD and window to enter the new process parameters

Figure 4. Optimization results.

The program allows optimization to be made manually or automatically. When done automatically the program tries to minimize the range for each parameter according to the specification. The process is iterative and some times takes a long time to complete. When the error is minimized the model card could be extracted.

These values are then used in the PSP Verilog-A model.

## III. SIMULATIONS

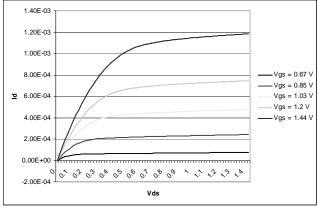

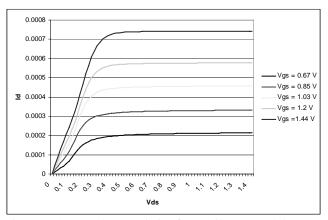

Simulations of the output transistor characteristics from the specific design kit library are given on Figure 5.

Figure 5. Output characteristics of the transistor from the technology library.

On Figure 6 the simulations of the output characteristic for Verilog-A model are presented.

Figure 6. Output characteristics for Verilog-A model.

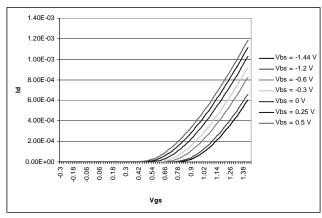

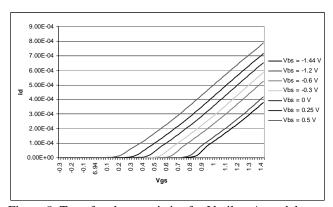

On figures 7 and 8 the simulation results of the transfer characteristics for transistor from the technology and the Verilog-A model are presented, respectively.

Figure 7. Transfer characteristics of the transistor from the technology library.

Figure 8. Transfer characteristics for Verilog-A model.

#### IV. CONCLUSIONS

A method for adaptation of the PSP Verilog-A code in CADENCE is suggested. A mechanism for extraction of the model parameters for a specific technology is presented. Extraction is aided by the Extract CAD tool. The process parameters that are not explicitly given in the technology specifications are calculated. Fitting of PSP parameters to technology parameters that are extracted through simulations is produced using the BSIM model of the given technology. Simulation results with the adapted Verilog-A PSP model prove to give acceptable predictions. The proposed method gives an opportunity for further finetuning of the predictions accuracy.

#### IV. ACKNOWLEDGEMENTS

This research was carried out within the framework of Contract Rila - 4/801 No. D002-20.03.12.2008

The authors would like to thank to Dr. Yiming Li's research group for providing the Extract CAD tool used.

### REFERENCES

- [1] G. Gildenblat, X. Li, H. Wang, W. Wu, R. van Langevelde, A.J. Scholten, G.D.J. Smit and D.B.M. Klaassen, "Introduction to PSP MOSFET Model", (Invited paper) *Workshop on Compact Modeling*, pp. 19-24, Anaheim CA, May 2005.

- [2] Y. Tsividis, "Operation and Modeling of the MOS Transistor", 2nd Edition, McGraw-Hill, New York, 1999. [3] G. Gildenblat, H. Wang, T.-L. Chen, X. Gu and X. Cai, "SP: an advanced surface-potential-based compact MOSFET model", IEEE JSSC, Vol. 39, Iss. 9, pp. 1394-1406, 2004.

- [4] R. van Langevelde, A.J. Scholten and D.B.M. Klaassen, http://www.semiconductors.philips.com/acrobat/other/philipsmodels/mos-models/model11/NLUR2002-802.pdf

- [5] H. Wang, T.-L. Chen and G. Gildenblat, "Quasi-static and nonquasi-static compact MOSFET models based on symmetric linearization of the bulk and inversion charges", *IEEE TED*, Vol. 50, Iss. 11, pp. 2262-2272, 2003.

- [6] H.Wang and G. Gildenblat, "A robust large signal non-quasi-static MOSFET model for circuit simulation", *in Proc.* 2004 IEEE CICC, pp. 5-8, 2004.

- [7] Dieter K. Schroder, *Semiconductor Material and Device Characterization*, Arizona State University, Wiley-IEEE Press 2006

- [8] http://pspmodel.asu.edu/

- [9] http://www.ymlab.org/software/ecad/psp/pspext.php